基于Virtuoso和NI AWR软件的RF前端模块集成设计流程

不断发展的通信标准(如LTE-A和5G)正在推动RF架构创新,因此,在小型化、性能和对通过提高频谱效率来提高数据吞吐量的技术支持方面,给RF前端模块设计带来了挑战。

为了满足多模和多频手机对更高性能和更小元件尺寸的需求,业界正在将模块集成策略从单一封装中的类似构建模块转换为采用基于多种技术的多功能前端。这些开发工作针对每个频率范围的、基于单个完全集成的RF模块产品,包括多模/多频功率放大器(PA)、双工器和RF开关等。

通常情况下,模块和子系统设计人员在设计中会使用多种技术。这些技术包括砷化镓(GaAs)和氮化镓(GaN)单片微波集成电路(MMIC),硅RFIC和多层层压板。每种技术都封装在一个特定的工艺设计套件(PDK)中,并会详细说明制造工艺和前端构建模块(组件库)的电气和物理属性。

支持多个PDK和电路/电磁(EM)协同仿真的多技术设计流程用于分析体声波(BAW)和表面声波(SAW)滤波器之间的电相互作用(基于等效电路模型)和多层层压封装。它可提供全面的模块分析和优化。但是,开发硅RFIC开关、低噪声放大器(LNA)和PA时,情况会有所不同,需要采用针对性更强的开发工具。

本文介绍了一种现代设计流程,它将PDK转换为可在NI AWR设计平台中进行仿真的流程,以支持芯片封装协同设计和EM验证。通过将设计 导入到可与PDK一起使用的动态库中,设计人员能够使用最初在完全不同的环境中创建的复杂设计,基于不同的技术有效地开发产品。

为特定需求设计的EDA工具

设计人员根据个人喜好和特定工具的功能,使用不同的射频EDA工具来处理单个或一组设计任务。一些工具专注于高频MMIC、PCB和模块设计,如Microwave Office电路设计软件。其他厂商,如Cadence的应用目标是基于硅的RFIC和模块设计。由于这些工具中的每一个都有各自的优势,因此最好采用那些支持互操作性和信息交换的设计流程,以便设计人员可以为每个设计任务选择最佳工具。

为了支持不同环境之间的数据交换,已经开发了几种行业标准文件格式,例如touchstone(SNP)和测量数据交换格式(MDIF)文件。touchstone文件提供S参数,即网络的小信号模拟或测量频率响应。MDIF文件允许通过无限数量的独立变量(如频率或栅极电压)对S参数或噪声等数据进行排序。这些格式允许设计人员在其仿真中对器件(例如RFIC或开关)的线性响应进行建模,并轻松地在设计工具之间来回传递该模型。

多谐波模型(有时也称为Keysight X参数)类似于S参数,增加了模拟大信号工作条件下的非线性行为的能力。在不同设计工具之间使用的其他数据格式包括用于电路块的Spice网表,用于原理图信息的交换文件格式(IFF),以及诸如GDSII和DXF的布局格式。

这些标准格式可以充分发挥作用,但它们各有其局限性。例如,S参数用于线性模拟,它们不适用于非线性模拟。一些RF模拟器只能使用双端口MDIF文件。大信号多谐波模型可能需要很长时间才能生成和模拟,文件往往很大,难以共享。而对于X参数来说,文件可以是千兆字节。

模块和子系统设计人员面临的挑战

对于集成了使用各种工具开发的多种技术的RF模块,由于整体设计任务的复杂性,对工具之间更大互操作性的需求往往超出简单的数据格式兼容性。前端模块和其他多技术设备可在单个层压模块上包含多达25个集成电路,包括BAW和SAW滤波器、III-V RF MMIC PA,以及具有多个天线的硅开关和硅LNA。在本文的设计实例中,硅开关和LNA是在Cadence工具中设计的,声学/层压滤波器是在Microwave Office软件中完成的。图1所示为典型的多芯片模块设计。

基于Virtuoso和NI AWR软件的RF前端模块集成设计流程图1:Microwave Office软件环境下的典型模块设计为交换机设计人员创建所有所需开关状态所需的文件非常耗时。该过程可能容易出错,因为需要支持RFIC涵盖的250多个状态。对于touchstone文件,仅捕获线性行为。对于开关甚至声学滤波器而言,至关重要的非线性行为需要由较大的多谐波文件捕获。随着RFIC分析和S参数文件生成,每个状态需要7分钟,而一个开关操作有68个状态,另一个有25个状态,这时,需要投入大量的时间,一般情况下,一个操作过程会花费数小时甚至数天。

Cadence Virtuoso和NI AWR软件协同仿真流程

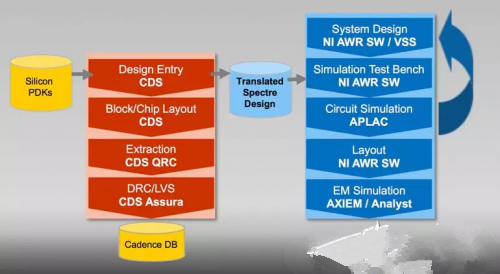

本文介绍的解决方案利用了直接在Microwave Office软件中支持Cadence设计的新功能。图2所示即为此流程。在这里,基于Microwave Office的Spectre网表转换的设计流程可以使Virtuoso和NI AWR软件协同仿真。

图2:NI AWR设计平台中用于协同仿真的Cadence Spectre转换流程通过采用硅工艺PDK并通过Spectre设计网表将其传输到Microwave Office软件中,设计人员可以访问所有NI AWR设计环境工具,从而实现该流程。这些工具包括Visual System Simulator(VSS)系统设计软件,Microwave Office线性和非线性仿真,APLAC谐波平衡和瞬态仿真,NI AWR布局工具,以及AXIEM 3D平面和Analyst 3D finite-element method (FEM)EM仿真器。

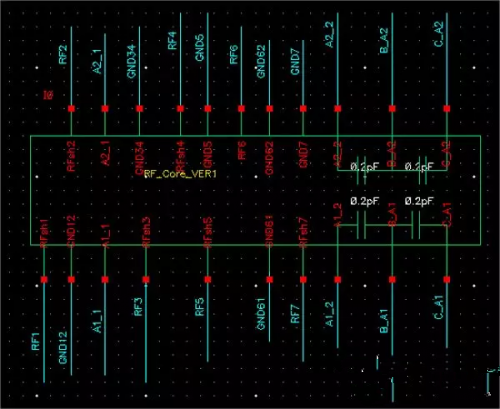

图3所示为具有片上滤波器的双极/八掷(DP8T)硅开关的Virtuoso原理图,其关键部件是天线开关模块(ASM),它有6种不同的开关状态。

网表和运行

使用“Netlist and Run”命令将创建NI AWR软件转换所需的文件。由于此命令是在测试平台运行的,因此要转换的实际上是一个子电路。创建的最关键文件是input.scs,其中包含所有相关的Cadence原理图信息。

运行“Import Spectre Netlist Design”脚本将打开一个简单的用户界面对话框。这种开关设计(大约2,000行网表)的翻译大约需要一秒钟。翻译完成后,可以在任何设计中使用两个组件:一个用于流程,另一个用于实际设计。

还要生成一个日志文件,为设计人员和设计支持团队提供有关已翻译的单元格,使用的库以及测试平台模拟的更详细信息。该转换包括原始设计中的微带线(MLIN)元素,它提供了设计中传输线中色散和损耗的精确建模。此外,还会捕获Cadence侧包含S参数块的任何文件的目录路径。

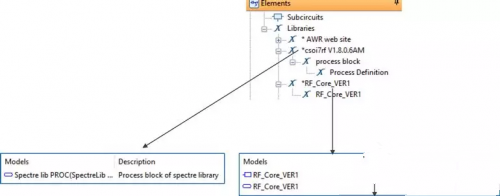

转换开关设计完成后,用户将两个新的PDK加载到Microwave Office软件中的新项目或现有项目中:翻译的Cadence代工厂PDK(csoi7rf Global foundries PDK,见图4左侧)和设计PDK(RF-Core,见图4右侧)。RF Core文件提供了原理图元素和设计块。这些PDK将提供模拟所需的三个简单的NI AWR软件库元素。

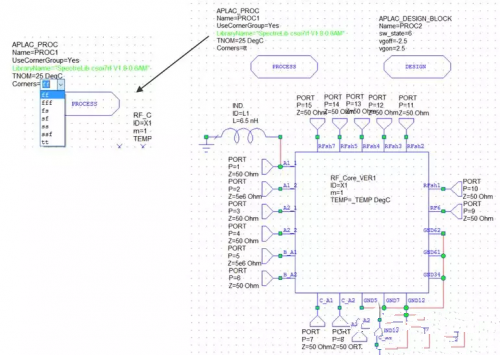

图4:翻译的Cadence代工厂PDK(左)和设计PDK(右)出现在元素树库中,可以插入任何NI AWR软件设计中新的库元素可通过标准“拖放”放置到Microwave Office电路设计软件原理图中,就像任何其他原理图元素一样。如图5中的原理图所示,PROCESS块用于引用代工厂PDK制程,并允许用户更改process corners。使用DESIGN块,用户可以访问Cadence设计中的任何设计变量。

图5:在此Microwave Office原理图中可以看到PROCESS块(代工厂PDK制程)和Cadence设计的设计变量的DESIGN块在图中右侧,翻译的组件有大约20个端口。DESIGN模块用来控制开关状态的位置(在本例中设置为6),以及控制开关状态的两个电压。左上角的PROCESS块(在图的左侧突出显示)为设计人员提供了指定process corners的能力,这对于IC设计非常重要。

为了验证在Microwave Office中模拟的网表转换与原始Spectre结果的频率响应,将测试用例Spectre模拟的S参数导入Microwave Office进行比较。验证设置实际上与包含已翻译网表的原理图测试台相同。对于此仿真,子电路包含直接从Cadence导出的touchstone S参数块。

比较小信号结果

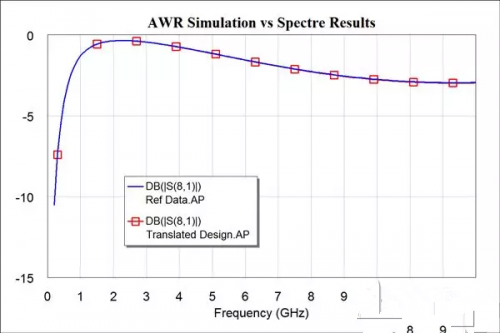

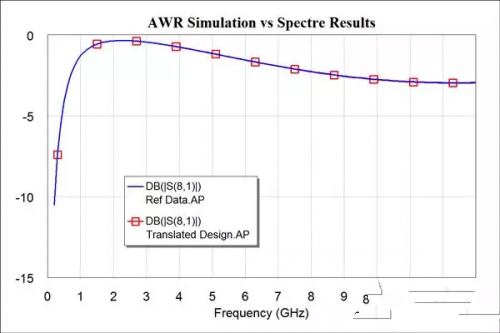

图6所示为NI AWR软件模拟的小信号结果与Spectre结果的比较情况,这由整个频带上的S参数表示。正如所料,结果显示两个结果确切一致。

图6:将NI AWR软件模拟的小信号结果与Spectre结果进行比较补充分析。

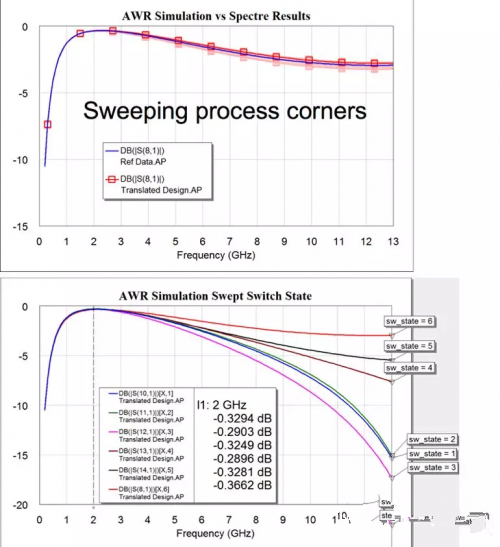

现在已经验证了设计转换,可以使用开关执行许多其他仿真,包括扫描process corners,调整/扫描开关状态,以及调整/扫描控制电压。导入的RFIC就像常规的Microwave Office元素一样。在图7的左侧,已将扫描process corners与直接从Cadence获取的参考数据进行比较,显示出了process corners的影响和模拟器之间的重叠。

图7:现在可以使用开关运行其他模拟,因为它的行为类似于常规的Microwave Office元素图7的右侧显示了在该示例中针对不同开关状态(通过路径)的模拟插入损耗。RFIC通过6种不同的开关状态进行控制,显示了取决于开关状态的不同响应。设计人员现在可以根据精确的RFIC模型开发层压板设计细节,通过参数设置轻松改变状态,可以实现调整或扫描。

此外,由于开关设计是常规的Microwave Office子电路,它可以与任何其他Microwave Office元件,EM结构,数据文件等组合。可以将多种技术组合到一个Microwave Office项目中,实现跨技术的协同仿真以及布局集成。单个叠层模块可以包含并组合硅开关、III-V PA RFIC、声学滤波器等。最终的集成设计布局包括声学滤波器、硅器件、GaAs-PA和模块。

分配布局

开关布局也可以以GDSII等标准格式从Virtuoso导出并导入NI AWR软件,然后可以与原理图子电路关联或链接,以确保正确的布局连接(见图8)。布局几何形状是相同的,颜色根据偏好而不同。

8:开关布局可以从Cadence Virtuoso导出并导入到NI AWR软件中,然后可以与原理图子电路关联或链接,以确保正确的布局连接结论。

本文介绍了一种集成设计流程,用于将源自不同软件工具的多种技术组合到一个项目中,实现仿真和布局设计工具之间的协同仿真。该流程不仅可以使设计人员集成不同的半导体和封装(层压)技术,还可以利用最初在RFIC设计环境中创建的复杂设计,并将其集成到专门用于MMIC、RF PCB和模块开发的设计环境中。最终的集成设计布局包括4种不同的技术:声学滤波器,硅器件,GaAs PA和模块。

登录

登录

注册

注册