芯片级电磁兼容性的设计方法及其应用

作者:殷和国 杨银堂 崔占东

来源:RFID世界网

日期:2007-03-30 10:23:24

摘要:随着系统越来越复杂,使用的频谱越来越宽。根据电磁兼容性学科多年的研究可知,分析和解决设备、子系统或系统间的电磁兼容性问题一般有三种方法:解决法、规范法和系统法。

1 引言

随着电子技术的迅速发展,现代电子设备已广泛应用于人类生活的各个领域。当前,电子设备已处于飞速发展时期,并且这个发展过程仍在日益增长着。电子设备的广泛应用和发展,必然导致它们在其周围空间产生的电磁场电平的不断增加。现代电子系统与当今电磁环境密不可分,电子设备不可避免地在电磁环境(EME)中工作。因此,人们面临的新问题,就是如何提高现代电子、电气设备或系统在复杂电磁环境中的生存能力,以保证达到电子系统初始的设计目的。正是在这种背景下产生了电磁兼容性的概念,形成了一门新的学科--电磁兼容性(EMC)研究。通常,电磁兼容被定义为某一电子系统在其电磁环境当中正常工作而不被这一环境过度干扰的能力。尤其对于作为现代电子系统主体的超大规模集成电路而言,电磁兼容性已成为影响其性能提高的瓶颈。因此,必须对这一领域进行研究以了解集成电路中辐射的产生方式及如何提高敏感度。电磁兼容性是一门关于抗电磁干扰(EMI)影响的科学,电磁兼容的中心课题是研究控制和消除电磁干扰,包括对电子系统的接地、屏蔽、滤波、正确选择无源元件和接点网络、整形电路、积分电路等电路技术,使电子设备或系统与其他设备联系在一起工作时,不引起设备或系统的任何部分的工作性能的恶化或降低。一个设计理想的电子设备或系统希望不受任何能量的影响。

2 分析和解决电磁兼容性的一般方法

随着系统越来越复杂,使用的频谱越来越宽。根据电磁兼容性学科多年的研究可知,分析和解决设备、子系统或系统间的电磁兼容性问题一般有三种方法:解决法、规范法和系统法。

2.1 解决法

解决法主要是在建立系统前并不专门考虑电磁兼容性问题,待系统建成后再设法解决调试过程中出现的电磁兼容性问题。系统内或系统间存在的干扰问题有三个:干扰源、接受器和干扰的传播路径。因此,解决系统内或系统间的电磁兼容性问题时,首先必须正确地确定干扰源,熟悉各种干扰源的特性,再确定干扰的耦合路径是辐射耦合模式还是传导耦合模式,最终决定消除干扰的方法。

2.2 规范法

为了满足电磁兼容性的要求,各国政府和工业部门尤其是军方都制订了很多强制执行的标准和规范,例如美国军用标准MIL-STD-461。所谓规范法是指在采购系统的设备和设计建立子系统时必须满足已制订的规范。规范法预期达到的效果就是,如果组成系统的每个部件都满足规范要求,则系统的电磁兼容性就能保证。

2.3 系统法

系统法集中了电磁兼容性方面的研究成果,从系统设计阶段的最初就用分析程序来预测将要遇到的电磁干扰问题,以便在系统设计过程中作为基本问题来解决。目前有下列几种已广泛使用的大规模电磁干扰分析程序:系统和电磁兼容性分析程序(SEMCAP);干扰预测程序IPP-1;系统内部分析程序IAP;共场地分析模型程序COSAM等。

对于EMC系统设计的三种方法而言,问题解决法是先建立系统,在系统出现EMC问题时,利用EMI抑制技术解决EMC问题,这种方法很冒险,有可能出现大量的返工;规范法则是要求每个分系统预先符合你所要求的EMC规范或标准,如你的产品需要销售到美国,就要求每个分系统满足美国FCC Part15或Part18相应的标准,利用这些标准进行计算、设计分系统来保证最终产品的EMC性能,规范法比问题解决法更合理,但它的不足之处是可能引入过储备的设计;系统法集中了EMC方面的成就,根据EMC的要求给出最佳的工程设计、试验过程中对EMC进行分析预测,合理分配EMC指标,保证系统EMC的设计要求。

随着电子设备工艺的飞速发展,集成电路的集成度几乎每年都翻一番,EMC问题已由系统级上升至芯片级,因此,对芯片级电磁兼容性的设计研究就显得尤为重要了。

3 芯片级电磁兼容

由于芯片级电磁兼容是一个相对较新的学科,尽管对于电子系统及子系统已经有了详细的标准和辐射参考标准,但对于在这些系统中应用到的集成电路来说却是一个空白。尤其是近年来集成电路的制造工艺已从超深亚微米(VDSM)进入到纳米阶段,加工芯片的特征尺寸进一步减小,越来越多的功能,甚至是一个完整的系统都能够被集成到单个芯片之中。这就使芯片级电磁兼容显得尤为突出。

3.1 芯片级电磁兼容的描述

附属于国际电工委员会(IEC)主要负责集成电路方面研究的机构正致力于研究集成电路电磁兼容性描述的两项标准。在不久的将来,我们就能根据 IEC61967标准来描述集成电路的电磁辐射;根据IEC62132标准来描述集成电路的抗扰度。尽管这两项标准中所描述的测量方法并不能够完全取代系统级的电磁兼容测量方法,但设计工程师将具备鉴别主要辐射源及在应用程序中哪一部分具有最低敏感度的能力。

目前,IEC61967标准,用于测量集成电路电磁辐射频率150kHz到1GHz,包括以下六个部分:通用条件和定义;辐射测量方法 --横向电磁波室法;辐射测量方法-- 表面扫描法;传导辐射测量方法--1Ω/150Ω直接耦合法;传导辐射测量方法--WFC(workbench faraday cage)方法;传导辐射测量方法--探磁针法。

IEC62132标准,用于测量集成电路电磁抗扰度,目前暂时包括以下五部分:通用条件和定义;辐射抗扰度测量方法 --横向电磁波室法;传导抗扰度测量方法--大量电流注入法(BCI);传导抗扰度测量方法--直接激励注入法(DPI);传导抗扰度测量方法 --传导辐射测量方法--WFC。

以上两项标准描述的测量方法可以被用作集成电路辐射和抗扰度规范说明的基础。当然,这些方法既有它们的优势,同时也存在局限性。因此,电子设备的设计者以及半导体生产商应谨慎地选择最符合其自身需求的测量方法。虽然我们能够用这些测量方法来描述芯片级集成电路的电磁兼容性,但我们不可能在系统级与芯片级测量方法之间进行直接比较。即使集成电路已经可以满足芯片级电磁兼容的需要,生产商仍需在整个系统中实现电磁兼容的测量。

通常,典型的电磁兼容测量方法,如过滤或屏蔽技术对于实现电子设备的电磁兼容性要求是必不可少的。至于在哪一部分实现电磁兼容性测量法,如在集成电路内或在印刷电路板上,则取决于成本及可行性方面,如可用空间等的考虑。

解决电磁兼容性问题,就是要查明并且减少实际的干扰源,其中一个最重要的解决芯片级电磁兼容的方法就是"表面扫描法 (IEC 61967-3)"。采用这种方法,能够使集成电路表面电磁场的实际磁场和电场形象化,同时,还能准确、容易地定位集成电路电磁辐射的干扰源。

3.1.1 表面扫描法

IEC 61967标准中的这一部分描述了评估集成电路表面近电场和近磁场元件的一种方法。这种方法适用的频率范围为10MHz到3GHz。为了测量这些场的分布状态,可以使电场探针或磁场探针机械地移过集成电路的表面(探针可以平行或垂直于集成电路表面)。测量数据可以通过计算机进行处理,并且,在一定的扫描频率下的场强能够用有色图谱形象地表示出来。运用这种方法所能达到的效果与机械探针配置系统的精度及所用探针的尺寸密切相关。此外,为了显示设计中的进展,可以对不同设计步骤进行比较。这一测量方法可以应用在任何一个集成在印刷电路板上、方便于使用探针测量的集成电路上。通过对集成电路表面进行电场和磁场扫描,能够得到关于电磁辐射源相对强度的相关信息。运用该方法 [16]可以准确地定位小片上集成电路封装内电磁辐射量过大的区域。

3.1.2 电场和磁场探针

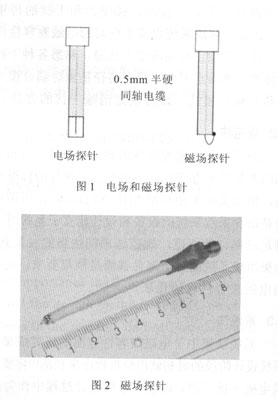

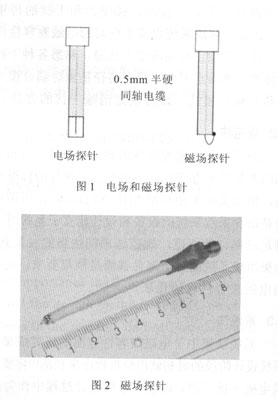

进行电场测量时,IEC61967-6 标准对具有部分屏蔽的微型电场探针的构造设计进行了规定;而对于磁场测量,这一标准则建议使用单向微型磁场探针。这两种探针都可用0.5mm的半刚体同轴电缆来制作,其有效的磁场探针孔径大约是200μm。图1示出了用同轴电缆制作的电场和磁场探针。图 2是一个磁场探针的实际外观。除了同轴电缆本身的屏蔽之外,为了改进探针的屏蔽效果,还需运用其他的屏蔽措施。

3.2 实际应用

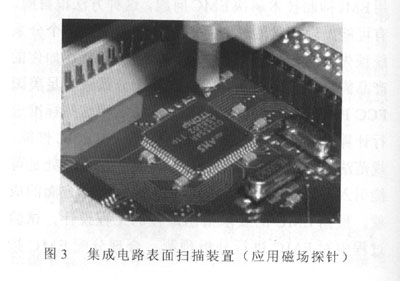

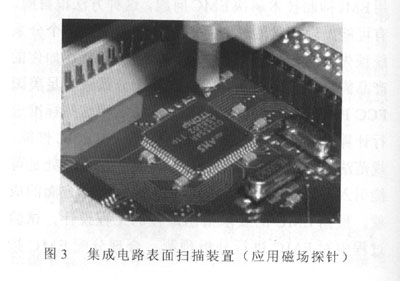

如图3所示,可以由一个微型位置调节器控制探针沿三个垂直方向线性移动进行表面扫描。为了扫描集成电路表面的矩形区域并用计算机处理所得到的测量数据,目前已开发出一种应用程序,可以使探针在集成电路表面之上沿正交面方向移动。

这一程序的扫描范围涵盖了X, Y,Z面,并且规定了光谱分析仪(用来测量电场或磁场探针输出电压的光谱)的各项参数。探针在集成电路表面沿一特定区域移动,并且在每一个测量点上从光谱分析仪获取频谱。这一程序能够给出所测电场或磁场的二维曲线。为了进一步处理所测量数据,可以将其保存为ASCII文件。典型的扫描小片步长为80mm,而扫描整个集成电路封装的步长为300 mm。最小的扫描步长既取决于芯片尺寸,也取决于配置系统的精确度。

探针也可以分别放置在小片或集成电路封装之上的任何位置,这就使得直接测量小片的特定部位的电磁辐射成为可能,如测量高速运算放大器。

图4给出了集成电路封装表面磁场扫描的示意图。从图中可以明显地看出具有较高的磁场强度元件的区域。由于高短路电流与高动态转换电流结合,故具有较高磁场辐射的管脚通常是集成电路的电源供应管脚和负载输出管脚。正是由于整个集成电路的电磁辐射主要集中在这些管脚上,所以电磁兼容性测量就应该从这里着手。

图5是用三维图形示出扫描区域磁场强度的测量结果。具有较高磁场强度的区域用红色(图上部较黑部分)突出出来,而具有较低磁场强度的区域用蓝色(图下面较黑部分)表示。对具有较高磁场强度区域有一定的了解之后,设计者就能够重新设计自己的电路以减少全局的电磁辐射。同时,版图工程师也可得到关键的提示,指导如何布置元件以降低辐射。

4 结束语

对于微电子行业来说,芯片级电磁兼容性的描述已经成为一个非常重要的主题。实际上,如果不对集成电路电磁辐射及抗扰度方面进行深入研究,就很难满足电子设备电磁兼容性方面的需要。随着工作频率及芯片复杂度的不断增长,具有低电磁辐射和高抗扰度的集成电路设计将越来越演变成具有挑战性的课题。将来,半导体生产商都将使用新标准(IEC 61967和IEC 62132)中不同的测量方法,来描述其集成电路的电磁辐射和抗扰度。而其中的"表面扫描法(IEC 61967-3)"可以被用来查明造成整个电磁辐射的主要干扰源。

今后应致力于芯片级电磁兼容性设计和优化,着重研究以下几个问题:更好地了解地面反射,进而了解普通模式电流是如何影响电磁辐射的,改进对辐射的控制;改进用于仿真的封装模型,改进芯片级电磁兼容的处理工具;减少信号完整性问题,提高防射频干扰的模拟模块和输入/输出模块的敏感度;减少封装产生的寄生参数,更好地控制输出信号的升降次数(适度的回转率)。

随着电子技术的迅速发展,现代电子设备已广泛应用于人类生活的各个领域。当前,电子设备已处于飞速发展时期,并且这个发展过程仍在日益增长着。电子设备的广泛应用和发展,必然导致它们在其周围空间产生的电磁场电平的不断增加。现代电子系统与当今电磁环境密不可分,电子设备不可避免地在电磁环境(EME)中工作。因此,人们面临的新问题,就是如何提高现代电子、电气设备或系统在复杂电磁环境中的生存能力,以保证达到电子系统初始的设计目的。正是在这种背景下产生了电磁兼容性的概念,形成了一门新的学科--电磁兼容性(EMC)研究。通常,电磁兼容被定义为某一电子系统在其电磁环境当中正常工作而不被这一环境过度干扰的能力。尤其对于作为现代电子系统主体的超大规模集成电路而言,电磁兼容性已成为影响其性能提高的瓶颈。因此,必须对这一领域进行研究以了解集成电路中辐射的产生方式及如何提高敏感度。电磁兼容性是一门关于抗电磁干扰(EMI)影响的科学,电磁兼容的中心课题是研究控制和消除电磁干扰,包括对电子系统的接地、屏蔽、滤波、正确选择无源元件和接点网络、整形电路、积分电路等电路技术,使电子设备或系统与其他设备联系在一起工作时,不引起设备或系统的任何部分的工作性能的恶化或降低。一个设计理想的电子设备或系统希望不受任何能量的影响。

2 分析和解决电磁兼容性的一般方法

随着系统越来越复杂,使用的频谱越来越宽。根据电磁兼容性学科多年的研究可知,分析和解决设备、子系统或系统间的电磁兼容性问题一般有三种方法:解决法、规范法和系统法。

2.1 解决法

解决法主要是在建立系统前并不专门考虑电磁兼容性问题,待系统建成后再设法解决调试过程中出现的电磁兼容性问题。系统内或系统间存在的干扰问题有三个:干扰源、接受器和干扰的传播路径。因此,解决系统内或系统间的电磁兼容性问题时,首先必须正确地确定干扰源,熟悉各种干扰源的特性,再确定干扰的耦合路径是辐射耦合模式还是传导耦合模式,最终决定消除干扰的方法。

2.2 规范法

为了满足电磁兼容性的要求,各国政府和工业部门尤其是军方都制订了很多强制执行的标准和规范,例如美国军用标准MIL-STD-461。所谓规范法是指在采购系统的设备和设计建立子系统时必须满足已制订的规范。规范法预期达到的效果就是,如果组成系统的每个部件都满足规范要求,则系统的电磁兼容性就能保证。

2.3 系统法

系统法集中了电磁兼容性方面的研究成果,从系统设计阶段的最初就用分析程序来预测将要遇到的电磁干扰问题,以便在系统设计过程中作为基本问题来解决。目前有下列几种已广泛使用的大规模电磁干扰分析程序:系统和电磁兼容性分析程序(SEMCAP);干扰预测程序IPP-1;系统内部分析程序IAP;共场地分析模型程序COSAM等。

对于EMC系统设计的三种方法而言,问题解决法是先建立系统,在系统出现EMC问题时,利用EMI抑制技术解决EMC问题,这种方法很冒险,有可能出现大量的返工;规范法则是要求每个分系统预先符合你所要求的EMC规范或标准,如你的产品需要销售到美国,就要求每个分系统满足美国FCC Part15或Part18相应的标准,利用这些标准进行计算、设计分系统来保证最终产品的EMC性能,规范法比问题解决法更合理,但它的不足之处是可能引入过储备的设计;系统法集中了EMC方面的成就,根据EMC的要求给出最佳的工程设计、试验过程中对EMC进行分析预测,合理分配EMC指标,保证系统EMC的设计要求。

随着电子设备工艺的飞速发展,集成电路的集成度几乎每年都翻一番,EMC问题已由系统级上升至芯片级,因此,对芯片级电磁兼容性的设计研究就显得尤为重要了。

3 芯片级电磁兼容

由于芯片级电磁兼容是一个相对较新的学科,尽管对于电子系统及子系统已经有了详细的标准和辐射参考标准,但对于在这些系统中应用到的集成电路来说却是一个空白。尤其是近年来集成电路的制造工艺已从超深亚微米(VDSM)进入到纳米阶段,加工芯片的特征尺寸进一步减小,越来越多的功能,甚至是一个完整的系统都能够被集成到单个芯片之中。这就使芯片级电磁兼容显得尤为突出。

3.1 芯片级电磁兼容的描述

附属于国际电工委员会(IEC)主要负责集成电路方面研究的机构正致力于研究集成电路电磁兼容性描述的两项标准。在不久的将来,我们就能根据 IEC61967标准来描述集成电路的电磁辐射;根据IEC62132标准来描述集成电路的抗扰度。尽管这两项标准中所描述的测量方法并不能够完全取代系统级的电磁兼容测量方法,但设计工程师将具备鉴别主要辐射源及在应用程序中哪一部分具有最低敏感度的能力。

目前,IEC61967标准,用于测量集成电路电磁辐射频率150kHz到1GHz,包括以下六个部分:通用条件和定义;辐射测量方法 --横向电磁波室法;辐射测量方法-- 表面扫描法;传导辐射测量方法--1Ω/150Ω直接耦合法;传导辐射测量方法--WFC(workbench faraday cage)方法;传导辐射测量方法--探磁针法。

IEC62132标准,用于测量集成电路电磁抗扰度,目前暂时包括以下五部分:通用条件和定义;辐射抗扰度测量方法 --横向电磁波室法;传导抗扰度测量方法--大量电流注入法(BCI);传导抗扰度测量方法--直接激励注入法(DPI);传导抗扰度测量方法 --传导辐射测量方法--WFC。

以上两项标准描述的测量方法可以被用作集成电路辐射和抗扰度规范说明的基础。当然,这些方法既有它们的优势,同时也存在局限性。因此,电子设备的设计者以及半导体生产商应谨慎地选择最符合其自身需求的测量方法。虽然我们能够用这些测量方法来描述芯片级集成电路的电磁兼容性,但我们不可能在系统级与芯片级测量方法之间进行直接比较。即使集成电路已经可以满足芯片级电磁兼容的需要,生产商仍需在整个系统中实现电磁兼容的测量。

通常,典型的电磁兼容测量方法,如过滤或屏蔽技术对于实现电子设备的电磁兼容性要求是必不可少的。至于在哪一部分实现电磁兼容性测量法,如在集成电路内或在印刷电路板上,则取决于成本及可行性方面,如可用空间等的考虑。

解决电磁兼容性问题,就是要查明并且减少实际的干扰源,其中一个最重要的解决芯片级电磁兼容的方法就是"表面扫描法 (IEC 61967-3)"。采用这种方法,能够使集成电路表面电磁场的实际磁场和电场形象化,同时,还能准确、容易地定位集成电路电磁辐射的干扰源。

3.1.1 表面扫描法

IEC 61967标准中的这一部分描述了评估集成电路表面近电场和近磁场元件的一种方法。这种方法适用的频率范围为10MHz到3GHz。为了测量这些场的分布状态,可以使电场探针或磁场探针机械地移过集成电路的表面(探针可以平行或垂直于集成电路表面)。测量数据可以通过计算机进行处理,并且,在一定的扫描频率下的场强能够用有色图谱形象地表示出来。运用这种方法所能达到的效果与机械探针配置系统的精度及所用探针的尺寸密切相关。此外,为了显示设计中的进展,可以对不同设计步骤进行比较。这一测量方法可以应用在任何一个集成在印刷电路板上、方便于使用探针测量的集成电路上。通过对集成电路表面进行电场和磁场扫描,能够得到关于电磁辐射源相对强度的相关信息。运用该方法 [16]可以准确地定位小片上集成电路封装内电磁辐射量过大的区域。

3.1.2 电场和磁场探针

进行电场测量时,IEC61967-6 标准对具有部分屏蔽的微型电场探针的构造设计进行了规定;而对于磁场测量,这一标准则建议使用单向微型磁场探针。这两种探针都可用0.5mm的半刚体同轴电缆来制作,其有效的磁场探针孔径大约是200μm。图1示出了用同轴电缆制作的电场和磁场探针。图 2是一个磁场探针的实际外观。除了同轴电缆本身的屏蔽之外,为了改进探针的屏蔽效果,还需运用其他的屏蔽措施。

3.2 实际应用

如图3所示,可以由一个微型位置调节器控制探针沿三个垂直方向线性移动进行表面扫描。为了扫描集成电路表面的矩形区域并用计算机处理所得到的测量数据,目前已开发出一种应用程序,可以使探针在集成电路表面之上沿正交面方向移动。

这一程序的扫描范围涵盖了X, Y,Z面,并且规定了光谱分析仪(用来测量电场或磁场探针输出电压的光谱)的各项参数。探针在集成电路表面沿一特定区域移动,并且在每一个测量点上从光谱分析仪获取频谱。这一程序能够给出所测电场或磁场的二维曲线。为了进一步处理所测量数据,可以将其保存为ASCII文件。典型的扫描小片步长为80mm,而扫描整个集成电路封装的步长为300 mm。最小的扫描步长既取决于芯片尺寸,也取决于配置系统的精确度。

探针也可以分别放置在小片或集成电路封装之上的任何位置,这就使得直接测量小片的特定部位的电磁辐射成为可能,如测量高速运算放大器。

图4给出了集成电路封装表面磁场扫描的示意图。从图中可以明显地看出具有较高的磁场强度元件的区域。由于高短路电流与高动态转换电流结合,故具有较高磁场辐射的管脚通常是集成电路的电源供应管脚和负载输出管脚。正是由于整个集成电路的电磁辐射主要集中在这些管脚上,所以电磁兼容性测量就应该从这里着手。

图5是用三维图形示出扫描区域磁场强度的测量结果。具有较高磁场强度的区域用红色(图上部较黑部分)突出出来,而具有较低磁场强度的区域用蓝色(图下面较黑部分)表示。对具有较高磁场强度区域有一定的了解之后,设计者就能够重新设计自己的电路以减少全局的电磁辐射。同时,版图工程师也可得到关键的提示,指导如何布置元件以降低辐射。

4 结束语

对于微电子行业来说,芯片级电磁兼容性的描述已经成为一个非常重要的主题。实际上,如果不对集成电路电磁辐射及抗扰度方面进行深入研究,就很难满足电子设备电磁兼容性方面的需要。随着工作频率及芯片复杂度的不断增长,具有低电磁辐射和高抗扰度的集成电路设计将越来越演变成具有挑战性的课题。将来,半导体生产商都将使用新标准(IEC 61967和IEC 62132)中不同的测量方法,来描述其集成电路的电磁辐射和抗扰度。而其中的"表面扫描法(IEC 61967-3)"可以被用来查明造成整个电磁辐射的主要干扰源。

今后应致力于芯片级电磁兼容性设计和优化,着重研究以下几个问题:更好地了解地面反射,进而了解普通模式电流是如何影响电磁辐射的,改进对辐射的控制;改进用于仿真的封装模型,改进芯片级电磁兼容的处理工具;减少信号完整性问题,提高防射频干扰的模拟模块和输入/输出模块的敏感度;减少封装产生的寄生参数,更好地控制输出信号的升降次数(适度的回转率)。

登录

登录

注册

注册